„Flipflop“ – Versionsunterschied

| [ungesichtete Version] | [ungesichtete Version] |

| Zeile 8: | Zeile 8: | ||

== Geschichte == |

== Geschichte == |

||

[[Datei:Eccles-Jordan trigger circuit flip-flip drawings.png|mini|upright=1.1|Flipflop aus der Patentschrift (1918)]] |

|||

[[Datei:Transistor Bistable interactive animated-en.svg|mini|upright=1.1|Bistabile Transistor-Kippstufe: Das Ausgangssignal liegt am Kollektor von Q2 gegen 0 V an.  (R3, R4 ⪆ 10× R1, R2)]] |

[[Datei:Transistor Bistable interactive animated-en.svg|mini|upright=1.1|Bistabile Transistor-Kippstufe: Das Ausgangssignal liegt am Kollektor von Q2 gegen 0 V an.  (R3, R4 ⪆ 10× R1, R2)]] |

||

Die Flipflopschaltung wurde 1918 von den Engländern [[William Henry Eccles]] und [[Frank W. Jordan]] an rückgekoppelten Radioröhrenverstärkern auf der Suche nach Zählschaltungen<ref>''Radio Review.'' Dez. 1919, S. 143 ff.</ref> entdeckt. Ursprünglich erhielt sie die Bezeichnung Eccles-Jordan-Schaltung.<ref>Zur Geschichte: Robert Dennhardt: ''Die Flipflop-Legende und das Digitale: eine Vorgeschichte des Digitalcomputers vom Unterbrecherkontakt zur Röhrenelektronik 1837–1945''. Kulturverlag Kadmos, Berlin 2009, Zugleich: Diss. Humboldt-Universität, Berlin 2007, ISBN 978-3-86599-074-7.</ref> |

Die Flipflopschaltung wurde 1918 von den Engländern [[William Henry Eccles]] und [[Frank W. Jordan]] an rückgekoppelten Radioröhrenverstärkern auf der Suche nach Zählschaltungen<ref>''Radio Review.'' Dez. 1919, S. 143 ff.</ref> entdeckt. Ursprünglich erhielt sie die Bezeichnung Eccles-Jordan-Schaltung.<ref>Zur Geschichte: Robert Dennhardt: ''Die Flipflop-Legende und das Digitale: eine Vorgeschichte des Digitalcomputers vom Unterbrecherkontakt zur Röhrenelektronik 1837–1945''. Kulturverlag Kadmos, Berlin 2009, Zugleich: Diss. Humboldt-Universität, Berlin 2007, ISBN 978-3-86599-074-7.</ref> |

||

Version vom 24. Juli 2018, 21:49 Uhr

Ein Flipflop (auch Flip-Flop), oft auch bistabile Kippstufe oder bistabiles Kippglied genannt, ist eine elektronische Schaltung, die zwei stabile Zustände des Ausgangssignals besitzt. Dabei hängt der aktuelle Zustand nicht nur von den gegenwärtig vorhandenen Eingangssignalen ab, sondern oft außerdem vom Zustand, der vor dem betrachteten Zeitpunkt bestanden hat. Eine Abhängigkeit von der Zeit besteht nicht, sondern nur von Ereignissen.

Durch die Bistabilität kann die Kippstufe eine Datenmenge von einem Bit über eine unbegrenzte Zeit speichern. Im Gegensatz zu anderen Speicherarten muss jedoch die Spannungsversorgung dauernd gewährleistet sein. Das Flipflop ist als Grundbaustein der sequentiellen Schaltungen ein unverzichtbares Bauelement der Digitaltechnik und damit fundamentaler Bestandteil vieler elektronischer Schaltungen von der Quarzuhr bis zum Mikroprozessor. Insbesondere ist es sehr häufig in bestimmten Ausführungen von Computerspeicher-Chips (statischen Speicherbausteinen) als elementarer Ein-Bit-Speicher enthalten.

Geschichte

Die Flipflopschaltung wurde 1918 von den Engländern William Henry Eccles und Frank W. Jordan an rückgekoppelten Radioröhrenverstärkern auf der Suche nach Zählschaltungen[1] entdeckt. Ursprünglich erhielt sie die Bezeichnung Eccles-Jordan-Schaltung.[2]

Charakteristik

Flipflops unterscheiden sich unter anderem

- in der Anzahl und der logischen Funktion ihrer Eingänge (beschrieben durch ihre charakteristische Gleichung oder Funktionstabelle),

- in der zeitlichen Reaktion auf die Eingangssignale (Daten- und Steuersignale), insbesondere auf die Taktsignale (Timing),

- in der Durchlässigkeit von Datensignalen bis zum Ausgang (Transparenz oder Momentanfreigabe)

- und im strukturellen Aufbau (einfache interne Mitkopplung oder Master-Slave-Prinzip).

Gemeinsam ist jedoch allen, dass sie zwei stabile Zustände haben, welche an einem Ausgang festgestellt werden können. Diese Zustände werden „gesetzt“ (set) und „zurückgesetzt“ (reset) genannt. Zwischen diesen Zuständen kann durch Signale an den Eingängen umgeschaltet werden. Üblicherweise ist neben dem Ausgang Q ein weiterer Ausgang Q vorhanden, an dem der negierte Wert von Q anliegt. Der Einschaltzustand ist bei einem einfachen Flipflop aus zwei symmetrisch angeordneten bipolaren Transistoren (wie im Bild rechts) nicht definiert. Dieser kann mittels eines Kondensators an einem der beiden Eingänge festgelegt werden.

Wird ein Flipflop zum Beispiel in Transistor-Transistor-Logik (TTL) aufgebaut, die mit 5 V gegen „Masse“ (0 V) betrieben wird, dann kann der Zustand „gesetzt“ durch eine Spannung von 2,4 bis 5 V (H-Pegel, HIGH) am Ausgang Q dargestellt werden. An dem negierten Ausgang Q liegen dann 0 bis 0,4 V (L-Pegel, LOW) an. Bei der Verwendung von positiver Logik wird dieser Zustand als Q = 1 und Q = 0 interpretiert. In dem Zustand „zurückgesetzt“ liegen die Werte vertauscht an den Ausgängen an (Q = 0 und Q = 1).– Genauso gut kann der L-Pegel als „gesetzt“ ansehen werden, der sich aus einem Anfangszustand mit H-Pegel abhebt. Das ist eine Frage der Willkür, die durchaus zweckmäßig sein kann. Dann wird mit negativer Logik gearbeitet, die allerdings innerhalb dieses Artikels nicht herausgestellt wird.

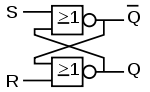

Das einfachste Flipflop ist das ungetaktete RS-Flipflop, welches die zwei Eingänge S und R besitzt. Über den Eingang S kann der Ausgang des Flipflops in den Zustand „gesetzt“ kippen (oder in diesem Zustand bleiben, falls er schon „gesetzt“ ist). Über den Eingang R kann das Flipflop in den Zustand „zurückgesetzt“ schalten. Die Eigenschaften des RS-Flipflops und anderer Flipflop-Arten werden weiter unten detaillierter erläutert.

Durch das Zusammenschalten mehrerer Flipflops entstehen leistungsfähige Systeme wie Register, Zähler (asynchron oder synchron), Datenspeicher (Halbleiterspeicher) und Mikroprozessoren. Flipflops sind Grundbausteine für die gesamte Digitaltechnik und Mikroelektronik von heute, einschließlich des Computers.

Klassifizierung anhand von Taktabhängigkeit

Nicht taktgesteuerte Flipflops

Der Zustand des oben eingeführten ungetakteten RS-Flipflops wird direkt durch die Pegel der Eingangssignale S und R bestimmt. Solche Flipflops nennt man asynchrone pegelgesteuerte (engl. level triggered) Flipflops. Es gibt aber auch die Möglichkeit, dass ein Flipflop seinen Zustand nur während eines Pegelwechsels der Eingangssignale ändert und der Pegel des Eingangssignals selbst keinen weiteren Einfluss hat. Solche Flipflops nennt man asynchrone flankengesteuerte (edge triggered) Flipflops. Zur praktischen Realisierung wurden früher Differenzierglieder verwendet. Heute werden die Signalflanken meist mit Hilfe von Laufzeitunterschieden intern in kurze Nadelimpulse verwandelt, oder sie werden direkt durch flüchtige interne Zustände ausgewertet.

Taktgesteuerte Flipflops

Da die Eingangssignale nur in bestimmten Zeitabschnitten stabil anliegen, ist es oft gewünscht, dass ein Flipflop nur zu bestimmten Zeiten auf die Eingangssignale reagiert. Dieses Verhalten kann durch Verwendung eines Taktsignals realisiert werden, das die Steuereingänge des Flipflops zu bestimmten Ereignissen freischaltet. Das Berücksichtigen eines Taktsignals ermöglicht auch Synchronität mit anderen Schaltungsteilen und die Bildung von synchronen Schaltkreisen. Hier gilt es zu unterscheiden, auf welche Weise ein Flipflop Taktsignale berücksichtigt. Das folgende Bild zeigt diesbezüglich, wie verschiedene Flipflop-Typen voneinander abhängen.

Taktzustands- und taktflankengesteuerte Flipflops

Taktgesteuerte Flipflops werden in synchronen Schaltwerken als Speicherelemente verwendet. Sie übernehmen ihre Daten- und Steuersignale durch ein (innerhalb des jeweiligen Schaltwerkes) einheitliches Taktsignal synchron und lassen sich in taktzustandsgesteuerte und taktflankengesteuerte Flipflops einteilen.

- Einfache taktzustandsgesteuerte Flipflops reagieren von der Anfangsflanke eines Taktimpulses bis zu seiner Endflanke auf die Eingangssignale. Sie werden einschließlich ihrer Änderungen zum Ausgang durchgereicht. Solche durch 1-Pegel oder 0-Pegel gesteuerte Bausteine sind transparent und vertragen keine Rückwirkung des Ausgangs auf den eigenen Eingang. Der Zustand zum Ende des Taktimpulses wird „gefangen“ und verwahrt. Das gibt dem Flipflop vor allem in der englischsprachigen Literatur die Bezeichnung Latch (was übersetzt „Riegel“ oder „Türschnapper“ bedeutet).

- Wird der Zustand dieses transparenten „Master-Flipflops“ mit der Endflanke des Taktimpulses in ein weiteres, das „Slave-Flipflop“, übergeben, so ist der Zustand hier von den Eingängen getrennt. Nur der Slave ist mit dem Ausgang verbunden; dessen Zustand ist also nichttransparent. Damit entsteht ein rückkopplungsfähiges „klassisches“ Master-Slave-Flipflop (z. B. Typ 7472), das als Zähl-Flipflop verwendet werden kann.

- Taktflankengesteuerte Flipflops können ihren Zustand nur während einer festgelegten Taktflanke ändern. Impulse, die solche Flanken enthalten, können aus den 0-Pegel in den 1-Pegel übergehen und wieder zum 0-Pegel zurückkehren, also mit steigender Flanke beginnen; sie können in anderen Fällen aus dem 1-Pegel in den 0-Pegel übergehen und wieder zurück zum 1-Pegel, also mit fallender Flanke beginnen (wie im ersten Bild). Das taktflankengesteuerte Flipflop reagiert nur während einer sehr kurzen Zeit nach der festgelegten Taktflanke auf die Signale, die an den Eingängen anliegen. In der übrigen Zeit bis zur nächsten Flanke in dieselbe Richtung bleibt der vorher eingestellte Zustand gespeichert und ändert sich – im Gegensatz zu zustandsgesteuerten Flipflops – auch dann nicht, wenn sich die Eingangssignale ändern. Es wird unterschieden in einflankengesteuerte Flipflops auf Wechsel bei steigender (positiver) Taktflanke oder bei fallender (negativer) Taktflanke sowie zweiflankengesteuerte (Übernahme am Eingang mit der einen, Ausgabe mit der anderen Taktflanke).

Flipflop-Typen

RS-Flipflop

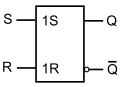

Ein RS-Flipflop (Rücksetz-Setz-Flipflop), auch SR-Flipflop genannt, ist die einfachste Art eines Flipflops. Grundelement dieser Schaltung ist eine bistabile Kippstufe ohne Taktsteuerung, wie es in der nachfolgenden Tabelle in der ersten Zeile gezeigt wird. Es verfügt über zwei Eingänge, die üblicherweise mit R und S bezeichnet werden. Mit geeigneter Zusatzbeschaltung können daraus sowohl taktpegelgesteuerte RS-Flipflops als auch taktflankengesteuerte RS-Flipflops generiert werden. Dann ist ein dritter, typischerweise mit C (Clock) bezeichneter Eingang vorhanden, an den ein Taktsignal angelegt werden kann. Diese RS-Flipflops dienen als Grundschaltungen zum Aufbau umfassenderer Flipflops.

Das Grundelement aus zwei Logikgattern (wie oben gezeigt) möge einen Ruhezustand mit R = S = 0 haben. Mit einem Signal S = 1 am „Setz“-Eingang und gleichzeitig R = 0 wird der Ausgang Q des Flipflops auf „logisch 1“ gesetzt. Mit der Zurücknahme dieser Anforderung durch S = 0 und gleichzeitig R = 0 verharrt das Flipflop infolge der Rückkopplung des Ausgangs auf das Eingangsgatter in dem zuvor eingestellten Zustand; er wird also gespeichert. Erst wenn der „Rücksetz“-Eingang aktiviert wird mit R = 1 bei S = 0, wird das Flipflop zurückgesetzt: Am Ausgang entsteht Q = 0. Auch hier ändert sich mit der Zurücknahme der Anforderung der Zustand nicht. Das Ausgangssignal im Falle R = S = 0 ist ungewiss, wenn nicht der vorherige Verlauf bekannt ist.

Die charakteristische Gleichung lautet (anhand der Schaltung mit NOR-Gattern)

Diese Gleichung ist mit den Mitteln der formalen Logik nicht nach Q auflösbar, womit das Speicherverhalten charakterisiert wird: Das Ausgangssignal ist abhängig von seiner Vorgeschichte.

Kritisch ist der Fall des Widerspruchs, wenn „Setzen“ und „Rücksetzen“ gleichzeitig angefordert werden mit R = S = 1 bzw. R = S = 0. Dieser in sich widersprüchliche (deshalb als „verboten“ bezeichnete) Zustand führt auf einen Fehler derart, dass an den beiden Ausgängen Q und Q eine 0 entsteht beim RS-Flipflop aus NOR-Gattern, dagegen an Q und Q eine 1 beim RS-Flipflop aus NAND-Gattern. Bei industriellen Steuerungssystemen sind Vorkehrungen zu treffen für den Fall, dass bei Betriebsstörungen der Widerspruch auftritt. Dazu muss bedacht werden, welcher der beiden Anforderungen „Setzen“ und „Rücksetzen“ das System in einen sicheren Zustand führt, wer also den Vorrang haben soll. Der Ausgang Q stellt sich bei der Schaltung mit NAND-Gattern auf Q = 1 ein; dieser Ausgang hat also Setzvorrang. Bei der Schaltung mit NOR-Gattern stellt sich Q = 0 ein; dieser Ausgang hat Rücksetzvorrang.

Oft wird behauptet, der Zustand R = S = 1 sei instabil oder unbestimmt; tatsächlich ist dieser Zustand völlig stabil. Unbestimmt ist lediglich der Nachfolgezustand beim (fast) gleichzeitigen Umschalten in den Speicherzustand mit R = 0 und S = 0. Dann hängt der Ausgangszustand davon ab, welches Signal (zufällig) zuletzt auf 0 springt und damit dominiert. Bei der Software-Realisierung von RS-Flipflops in speicherprogrammierbaren Steuerungen ist die Reihenfolge in der Befehlseingabe zu beachten. In der Programmabarbeitung wird der zuletzt ausgeführte Befehl der dominante. Innerhalb von Multitaskingsystemen muss daher die Abarbeitung des Setzens und Rücksetzens gekapselt sein und darf nicht unterbrochen werden. Dominierende RS-Flipflops als einzelne Hardwarebausteine waren nicht erhältlich. Die Dominanz kam nur indirekt dann zum Einsatz, wenn ein komplexer Baustein mit Reset- und Set-Eingängen ausgestattet war.

Die Arbeitsweise einer RS-Kippstufe lässt sich mit der einer mechanischen Wippe vergleichen, deren Schwerpunkt höher liegt als der Drehpunkt. Durch diesen Aufbau entsteht eine Mitkopplung wie in der Gatter-Schaltung; die Wippe nimmt dann eine von zwei möglichen stabilen Endlagen ein, ohne dass vorher klar ist, welche das sein wird. Sie kann aber durch Anstoßen unbefristet in die eine oder andere gewünschte Endlage gebracht werden. Eine Mittellage ist in einem binären System nicht möglich. (Ein Verharren im labilen Gleichgewicht – wie sich das bei der mitgekoppelten Wippe infolge Reibung mit Mühe einstellen lässt – entfällt beim Flipflop.)

In der folgenden Zusammenstellung ist die obere Abteilung mit negierten Zeichen S und R am Eingang ausgeführt. Das heißt, dass der Ruhezustand der Eingangssignale durch den 1-Pegel gebildet wird, und der aktive, schaltende Zustand durch 0-Pegel der Eingänge. Das ist durch den Aufbau des Flipflops aus NAND-Gattern bedingt und durchaus in der Praxis üblich. Das gilt insbesondere bei TTL-Bausteinen, bei denen sich ein offener Eingang verhält wie an 1-Pegel gelegt. Bei der unteren Abteilung werden die Eingänge durch die Freigabestufe negiert, so dass hier wieder mit den nicht negierten Zeichen gearbeitet wird. Die Signal-Zeit-Diagramme sind zu positiver Logik gezeichnet: Ein 1-Pegel wird durch den oberen Zustand (HIGH) dargestellt, ein 0-Pegel durch den unteren (LOW).

| Name und Schaltsymbol |

Signal-Zeit-Diagramme | Ersatzschaltbild | Funktionstabelle | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Asynchrones RS-Flipflop |

Standardverhalten | Logik-Schaltung eines RS-Flipflops aus zwei NAND-Gattern |

Die Eingänge des Flipflops sind hier negiert: R und S. Ihr (aktives) Rücksetzen bzw. Setzen führen sie mit 0 aus.

| ||||||||||||||||||||||||

|

|

| |||||||||||||||||||||||||

| RS-Flipflop mit Taktpegelsteuerung |

Verhalten mit Freigabe von R und S durch H-Pegel an clock |

Logik-Schaltung eines getakteten RS-Flipflops aus vier NAND-Gattern |

| ||||||||||||||||||||||||

|

|

|

D-Flipflop

Taktflankengesteuertes D-Flipflop

Das D-Flipflop (abgekürzt für Data- oder Delay-Flipflop) dient zum „Verzögern“ des Signals am Dateneingang bis zur Freigabe synchron zu einer Taktflanke. Es besitzt einen Dateneingang D und einen dynamischen Eingang C (Clock), der im Schaltsymbol mit gekennzeichnet wird, wenn er auf steigende Flanke reagiert. (Wenn eine fallende Flanke die aktive ist, wird noch ein Negierungszeichen außerhalb der Symbolkontur davorgesetzt.) Dieses D-Flipflop realisiert die elementare charakteristische Funktion der taktgesteuerten direkten Übernahme des Dateneingangs zum Ausgang

Darin gilt D für den Zustand bis zur Triggerung und Q' nach der Triggerung. Bis zur nächsten aktiven Taktflanke wird der aktuelle Zustand gehalten („verzögert“). Die gegenläufige Flanke hat keinen Einfluss.

| Eingänge | Ausgang | ||

|---|---|---|---|

| C | D | Q | |

| 0 | 0 | ||

| 1 | 1 | ||

| 0, 1, | X | unverändert | |

| = steigende Flanke X = beliebig, 0 oder 1 | |||

Dieses Verhalten führt auf zwei wichtige Anwendungen:

- Speicherung eines Datenbits solange, bis der Takteingang eine neue Speicherung auslöst und

- Synchronisierung paralleler, gleichzeitig begonnenener Vorgänge, die je nach Anzahl und Art der durchlaufenen Bauelemente unterschiedlichen Laufzeitverzögerungen unterliegen.

Weil sich alle Änderungen an D, die nach der aktiven Flanke eintreffen, erst zur nächsten aktiven Flanke auswirken, ist es nichttransparent und als elementares Flipflop direkt rückkopplungsfähig. Beispielsweise ist eine Verbindung von Ausgang Q zum Eingang D derselben Kippstufe zulässig, durch die sich das Ausgangssignal in sein Gegenteil ändert, aber immer erst zur nächsten aktiven Taktflanke. Damit eignet sich das D-Flipflop zum Grundbaustein von Zählschaltungen. Durch Zusammenschluss mehrerer solcher Kippglieder und äußere Beschaltung lassen sich – wie mit weiteren taktflankengesteuerten Flipflops − umfangreiche Schaltungen wie Synchronzähler, Frequenzteiler oder Schieberegister realisieren.

Mit einem Clock-Enable-Eingang CE (im deutschsprachigen Raum „Vorbereitungseingang“ V) kann der Takteingang in seiner Funktion freigeschaltet werden (engl. enable = freigeben); ohne Freigabe bleibt der Zustand bis zu einer späteren Taktflanke unverändert. In dieser Ausstattung wird das Flipflop als DV-Flipflop bezeichnet.

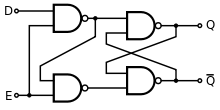

Taktpegelgesteuertes D-Flipflop

Alternativ können D-Flipflops neben dem Dateneingang D einen statischen Eingang E enthalten, der auf Pegel reagiert. Diese Kippstufe ist ein typisches Latch. Dafür gilt die angegebene Funktionstabelle. Darin bedeutet X einen beliebigen Logikpegel und Q0 den letzten D-Pegel vor E = 0.

| Eingänge | Ausgang | ||

|---|---|---|---|

| E | D | Q | |

| 1 | 0 | 0 | |

| 1 | 1 | 1 | |

| 0 | X | Q0 | |

Das D-Latch besteht aus einem RS-Flipflop und davor einer unsymmetrischen Eingangsbeschaltung. Mit dieser wird der „verbotene“ Zustand R = S = 1 vermieden. Solange der (meist mit dem Takt beschaltete) Freigabeeingang auf E = 1 liegt, erscheinen die Daten am Eingang D unmittelbar am Ausgang Q. In diesem Zustand ist das D-Latch transparent. Für den Rest einer Taktperiode bleibt das Datenbit noch verfügbar, während sich das Eingangssignal bereits ändern kann.

JK-Flipflop

JK-Flipflops wurden wahrscheinlich nach Jack Kilby benannt; gelegentlich werden sie Jump-/Kill-Flipflops genannt. Sie sind flankengesteuert oder als Master-Slave-Flipflop ausgeführt. Der Eingang C kann für steigende Flanken (Wechsel von 0 auf 1) oder für fallende Flanken (Wechsel von 1 auf 0) ausgelegt werden. Mit dem Taktsignal und der Eingangsbelegung J = 1 und K = 0 wird am Ausgang eine 1 erzeugt und gespeichert, alternativ bei K = 1 und J = 0 eine 0. Der Zustand J = K = 1 ist erlaubt. In diesem Fall wechselt der Ausgangspegel mit jeder wirksamen Flanke des Taktsignals,– ein Verhalten das die Bezeichnung als Toggle-Flipflop zulässt. Für J = K = 0 bleibt der letzte Ausgangszustand erhalten. Die charakteristische Gleichung lautet (mit J, K, Q bis zur Flanke und Q' nach der Flanke)

Bei der Realisierung des JK-Flipflops als taktzustandsgesteuertem Master-Slave-Flipflop muss als wesentliche Einschränkung beachtet werden, dass sich bei aktivem Taktzustand die Zustände der beiden Eingänge J und K nicht mehr ändern dürfen. Dann liegt also kein rein taktflankengesteuertes Flipflop vor. Dieser Nachteil ist auch ein Grund, warum sie als Master-Slave-Flipflops in komplexen Digitalschaltungen nur noch selten verwendet werden und primär durch flankengetriggerte Flipflops ersetzt werden, die diesen Nachteil nicht aufweisen.

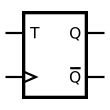

T-Flipflop

Synchrones T-Flipflop

| T | Qn | |

|---|---|---|

| 0 | Qn-1 | unverändert |

| 1 | Qn-1 | gewechselt |

Das synchrone T-Flipflop besitzt neben dem dynamischen C-Takteingang einen T-Eingang. T steht dabei für toggle – hin- und herschalten. Es zeigt ein Wechselverhalten synchron zur aktiven Flanke immer dann und nur dann, wenn T = 1 ist. Es kann aus einem flankengesteuerten JK-Flipflop gebildet werden, indem J- und K-Eingang verbunden werden und gemeinsam als T-Eingang fungieren. Das synchrone T-Flipflop wird beispielsweise in Synchronzählern verwendet. Sein Verhalten wird durch die angegebene Tabelle beschrieben. Darin bedeutet Qn den Zustand des Flipflops nach der n-ten aktiven Taktflanke.

Asynchrones T-Flipflop

Wird der T-Eingang fest auf „1“ gelegt, so bekommt der bisherige Takteingang C die Funktion eines Signaleingangs. Da keine Anbindung an einen Takt gegeben ist, wird diese Ausführung als asynchrones T-Flipflop bezeichnet. Obwohl das Eingangssignal nicht periodisch auftreten muss, wird es teilweise ebenfalls Taktsignal genannt.

Die erste Realisierung eines Toggle-Flipflops in elektromechanischer Bausteinform wurde schon im 19. Jahrhundert als Stromstoßschalter („Eltako“) für die Tasterschaltung (Treppenhausschaltung ohne Zeitschalt-Funktion) prominent und ist heute noch bei Neuinstallationen verbreitet im Einsatz. Das asynchrone T-Flipflop kann durch ein taktflankengesteuertes D-Flipflop gebildet werden, wenn dessen Ausgang Q auf den Eingang D zurückgeführt wird.

Bei periodischem Eingangssignal erfährt das Ausgangssignal durch das Hin- und Herschalten eine Halbierung der Frequenz (Frequenzteilung durch 2); dementsprechend dienen diese Flipflops vor allem als Grundelement in asynchronen binären Zählern und auch in dezimalen Frequenzteilern und Frequenzzählern. Ferner werden sie verwendet, wenn ein Rechtecksignal mit einem Tastverhältnis von exakt 1:1 gewonnen werden soll, wenn nur ein unsymmetrisches Signal, aber von doppelter Frequenz, zur Verfügung steht.

Zusätzliche asynchrone Steuereingänge bei Flipflops

Je nach Bauart besitzen die getakteten Flipflops (taktzustands- und auch taktflankengesteuerte Flipflops) zusätzliche Eingänge für asynchrone Steuersignale. Diese beeinflussen das Flipflop unabhängig vom Taktsignal. Je nach Bauart besitzen diese Bauelemente einen zusätzlichen Reset-Eingang R, einen Set-Eingang S oder beide. Das Reset wird manchmal auch als „Clear“ (Löschen) bezeichnet, das Setzen als „Preset“ (Vorbelegen). Häufig werden die beiden zusätzlichen Eingänge auf LOW-aktive Ansteuerung ausgelegt und dann mit S und R bezeichnet.

Durch den asynchronen Reset-Eingang kann das Flipflop in den Anfangszustand Q = 0 (Reset-Zustand) gebracht werden. Diese Funktion wird beispielsweise beim Einschalten der Versorgungsspannung verwendet oder wenn die Schaltung während des Betriebs erneut in den Anfangszustand gebracht werden muss. Der Set-Eingang entspricht im Verhalten dem Reset-Eingang, bringt aber das Flipflop in den Setz-Zustand Q = 1. Eine gleichzeitige Betätigung des asynchronen Setz- und Rücksetzeingangs ist „verboten“.

Timing der Flipflops

Bei zeit-kritischen Anwendungen der Flipflop-Bauelemente in Elektronik-Schaltungen müssen verschiedene Vorgaben beachtet werden. Als Beispiel wird hier ein taktflankengetriggertes D-Flipflop mit Einflankentriggerung betrachtet. Als Referenz für jeden einzelnen Schaltvorgang wird die aktive Schaltflanke des Takts (Clk) verwendet.

Das Eingangssignal (Data) des Flipflops darf sich vor der aktiven Schaltflanke des Taktsignals für eine definierte Mindestdauer nicht ändern. Diese Zeit wird als Setup-Zeit (engl. setup-time) bezeichnet. Entsprechend darf sich der Logikzustand am D-Eingang nach der aktiven Schaltflanke des Taktsignals für eine definierte Mindestdauer ebenfalls nicht ändern. Diese Zeit wird als Haltezeit (engl. hold-time) bezeichnet. Bis sich nach der Flanke das Ausgangssignal eingestellt hat, ist die Signallaufzeit durch das Bauelement (engl. propagation delay time) zu beachten.

Die garantierte Frequenz des Taktsignals darf nicht überschritten werden. Ferner darf die Mindest-Pulsbreite (engl. pulse-width) des Taktsignals nicht unterschritten werden. Diese wird ab der aktiven Taktflanke bis zur umgekehrten Taktflanke des Impulses gezählt. Bei Flipflops mit zusätzlichen asynchronen Steuereingängen dürfen sich die Steuersignale ebenfalls für eine definierte Mindestzeit vor der aktiven Taktflanke des Taktsignals und für eine definierte Mindestdauer hinterher nicht ändern. Wenn die Timing-Vorgaben nicht eingehalten werden, kann davon ausgegangen werden, dass es zu Fehlfunktionen bei den Flipflops kommt.

Alle anderen Flipflops mit Takteingang haben grundsätzlich dasselbe Verhalten wie das D-Flipflop. Beim JK-Flipflop müssen zusätzlich eine Setupzeit und eine Haltezeit für J- und K-Eingang eingehalten werden. Auch für das RS-Flipflop gelten Zeitvorgaben.

Schaltzeichen verschiedener Flipflop-Typen

Verwendung von Flipflops

Bei den eingangs zu den einzelnen Typen aufgeführten Anwendungen sind Flipflops typischerweise Teil eines größeren Elektronikbauelements. In der professionellen Schaltungsentwicklung werden Flipflops heute kaum noch als Einzelbauelemente eingesetzt. Heute werden typischerweise Bauelemente eingesetzt, die neben Flipflops aus weiteren Schaltungsfunktionen in einem gemeinsamen Bauelement bestehen. Hierunter fallen unter anderem auch FPGA-, PLD- und ASIC-Bauelemente. In diesen Bauelementen sind typischerweise D-Flipflops enthalten.

Literatur

- Manfred Seifart, Helmut Beikirch: Digitale Schaltungen. Verlag Technik, Berlin 1998, ISBN 3-341-01198-6.

- Gerd Scarbata: Synthese und Analyse Digitaler Schaltungen. Oldenbourg Wissenschaftsverlag GmbH, München 2001, ISBN 3-486-25814-1.

Weblinks

- Flipflops interaktiv (Java erforderlich)

- Interaktive Simulation von verschiedenen Flipflop-Typen mit dem Hades simulation framework (englisch)

- Interaktive LogiFlash-Animationen (Rubrik „2 Speicherglieder“)

- Mehr Informationen zu RS- und JK-Flipflops (Homepage deutsch/englisch)

- Wikibooks – Digitale Schaltungstechnik zum Thema FlipFlops

Einzelnachweise

- ↑ Radio Review. Dez. 1919, S. 143 ff.

- ↑ Zur Geschichte: Robert Dennhardt: Die Flipflop-Legende und das Digitale: eine Vorgeschichte des Digitalcomputers vom Unterbrecherkontakt zur Röhrenelektronik 1837–1945. Kulturverlag Kadmos, Berlin 2009, Zugleich: Diss. Humboldt-Universität, Berlin 2007, ISBN 978-3-86599-074-7.